Zero ASIC ·

Bring Your Own RTL to Zero ASIC’s Chiplet Ecosystem

Today, Zero ASIC is releasing a demo that shows how to create a custom EBRICK, a chiplet that can plug into our SiP design ecosystem. The demo can be found on GitHub at https://github.com/zeroasiccorp/ebrick-demo.

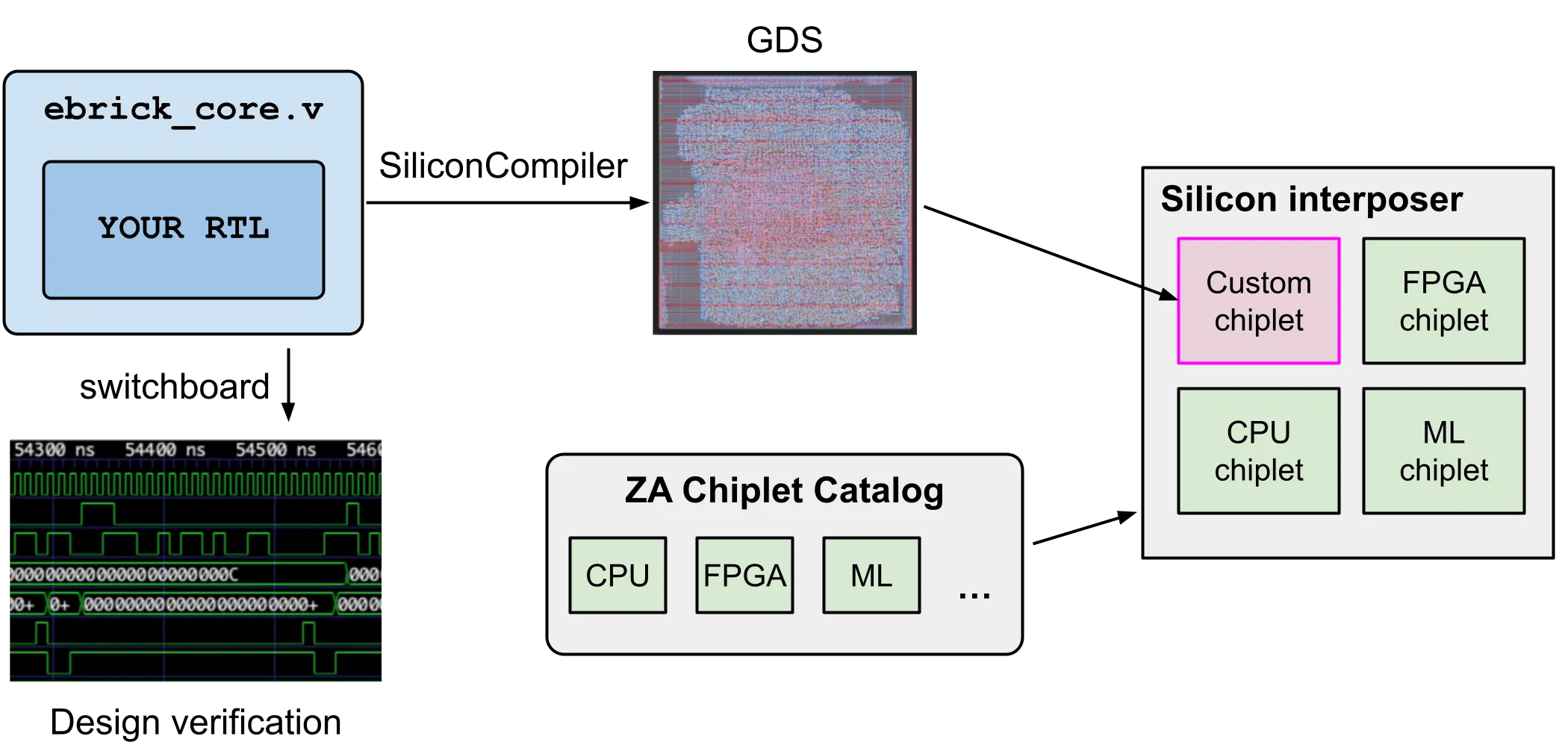

EBRICKs are chiplets with a standard interface and standard sizes, making it possible to mix and match them on a general-purpose silicon interposer. Zero ASIC is currently developing a catalog of standard EBRICKs, including a RISC-V CPU, a machine learning accelerator, and an FPGA. By combining these standard chiplets with a custom EBRICK containing the “secret sauce” for an application, high-performance hardware products can be developed in a cost- and time-efficient manner.

In the demo, we show how our tools switchboard and SiliconCompiler make it easy to verify a custom EBRICK design and generate a physical implementation. The intent is that the demo repository may be used as a template for building custom EBRICKs, where the demo logic is replaced with a user’s custom logic.

Design Architecture

The EBRICK design flow starts by instantiating custom RTL in an ebrick_core module definition. The ebrick_core interface is standardized, consisting of an array of UMI ports and GPIO interfaces. This is effectively the contract for creating a chiplet that can plug into our ecosystem.

The demo uses the PicoRV32 RISC-V processor as a small example of custom RTL. PicoRV32 has an AXI-Lite port, while the ebrick_core interface has UMI ports, so we use the axilite2umi module from the UMI repository to bridge between the two. The whole ebrick_core implementation comes out to a few hundred lines of Verilog, including comments, tie-offs, etc.

Verification

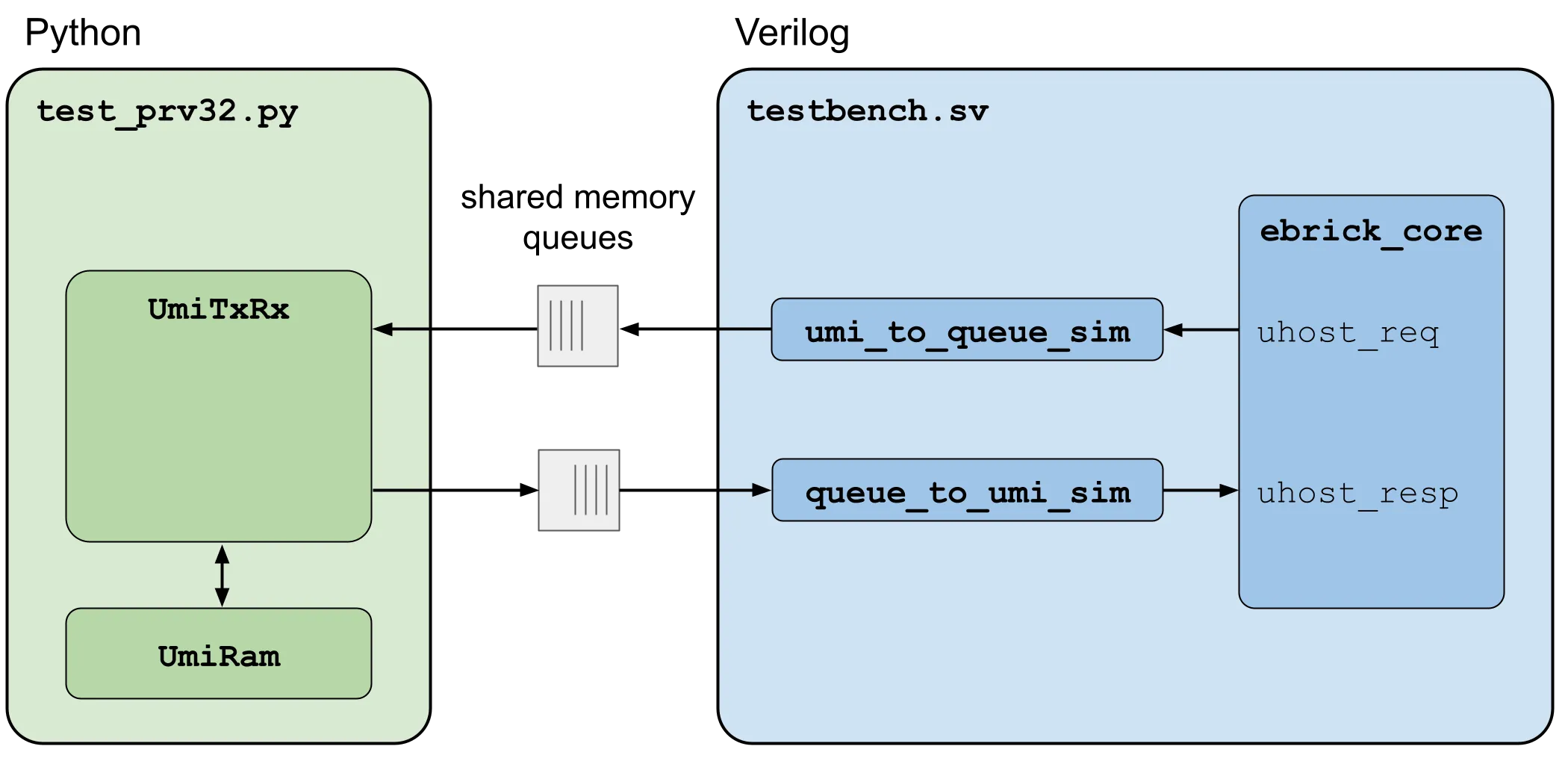

Once ebrick_core integration is completed, the design can be tested using switchboard. On the Verilog side of the test setup, the custom ebrick_core module is connected to modules that convey its UMI transactions to/from shared memory queues. On the Python side, a UmiTxRx object sends UMI packets to and receives UMI packets from these shared memory queues. A processing loop in Python inspects incoming packets and forwards memory transactions to an instance of UmiRam, a software model of UMI memory.

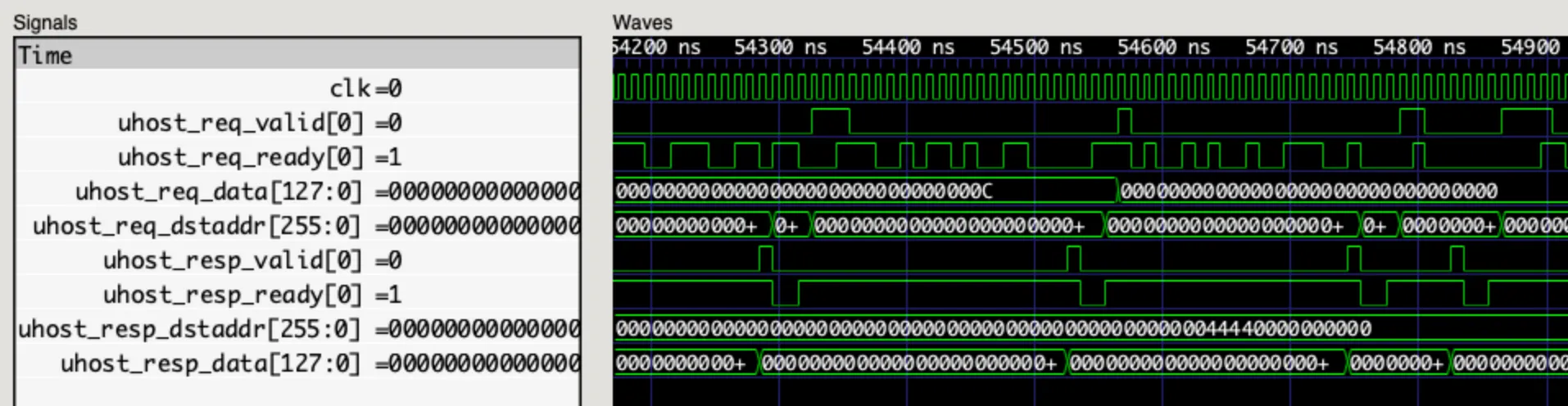

We show that this setup can be used to run a “hello world” RISC-V binary on the PicoRV32 EBRICK. The waveforms below show memory transactions recorded during program execution, with requests sent out by PicoRV32 (uhost_req_*) and responses sent back by the external memory (uhost_resp_*).

Physical Implementation

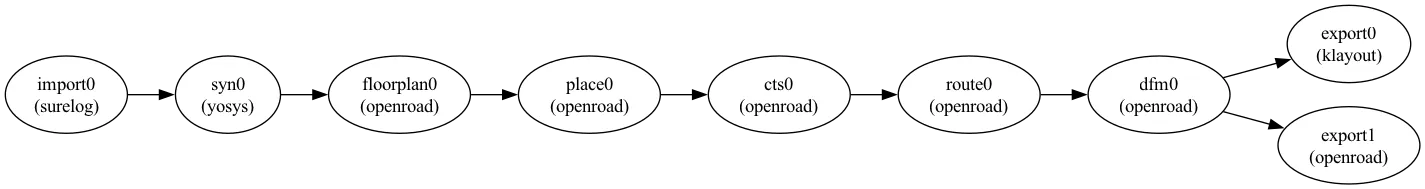

EBRICK physical implementation is powered by SiliconCompiler. The demo supports two open-source PDKs, ASAP7 and SKY130, using a build flow constructed from open-source tools:

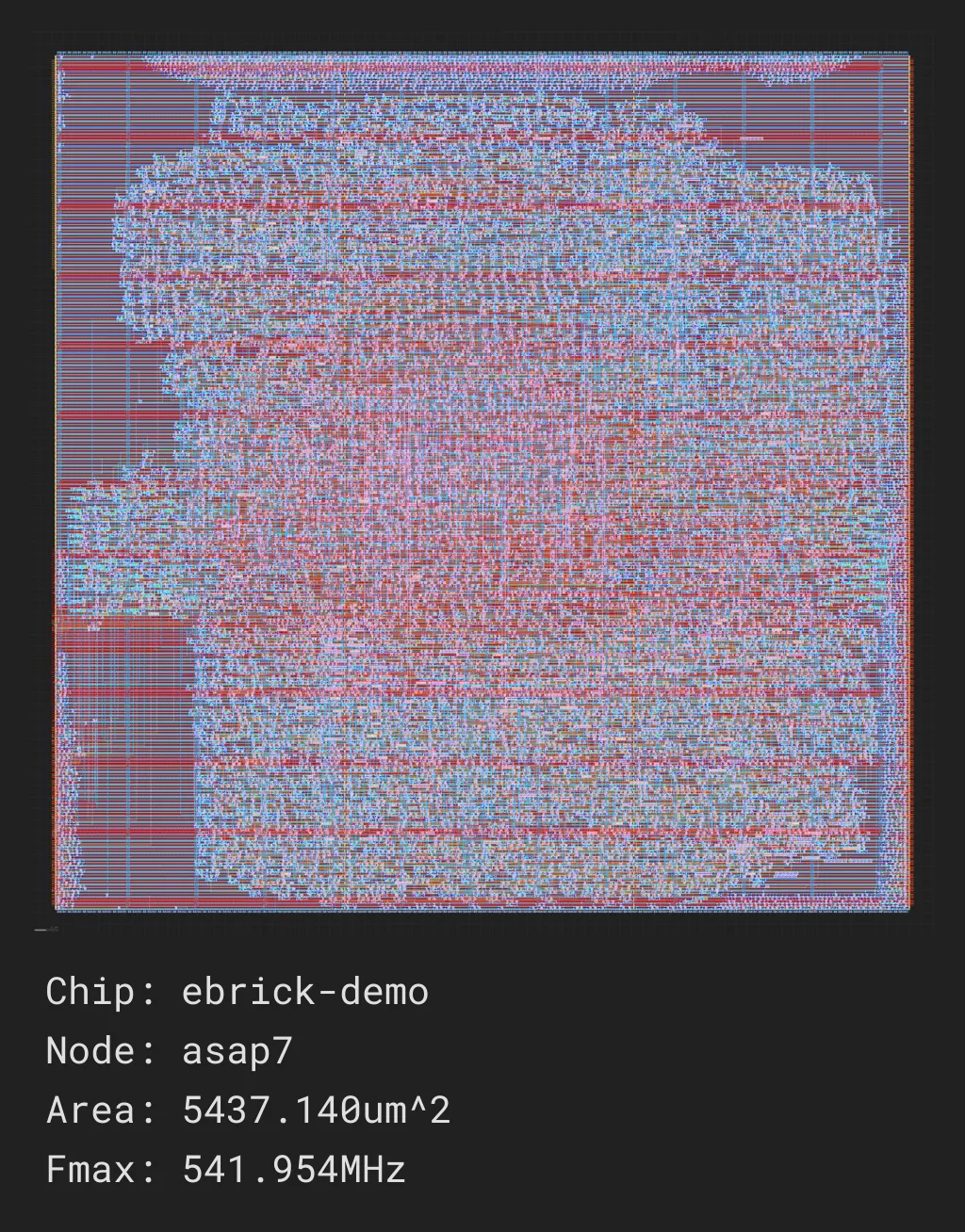

Thanks to the high level of automation provided by SiliconCompiler, process-specific differences in the build setup are minimal: about a dozen lines each of TCL constraints and Python commands.

Here’s what the GDS output looks like for ASAP7:

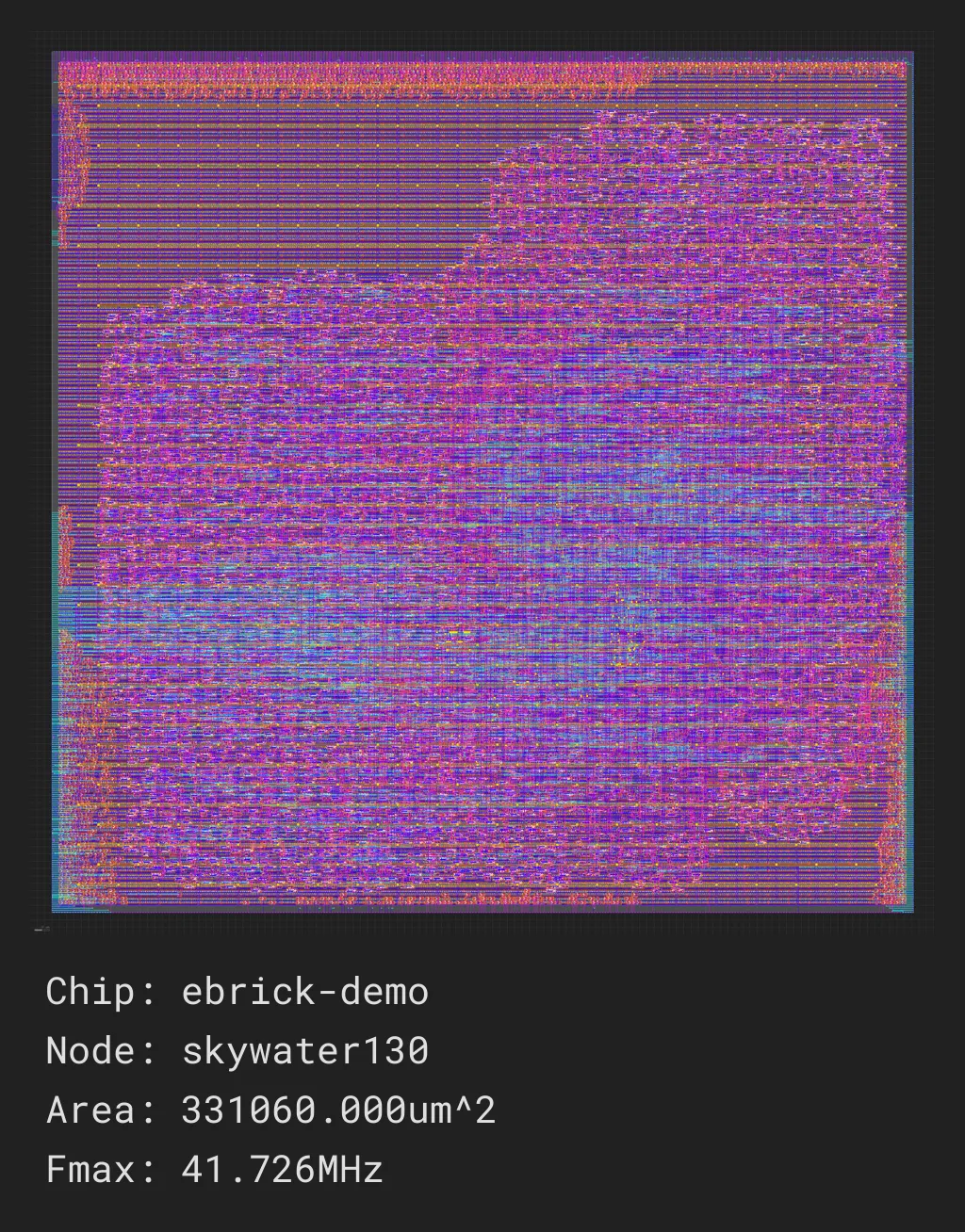

For SKY130: