Zero ASIC ·

Switchboard: An Open Source High-Performance Communication Platform

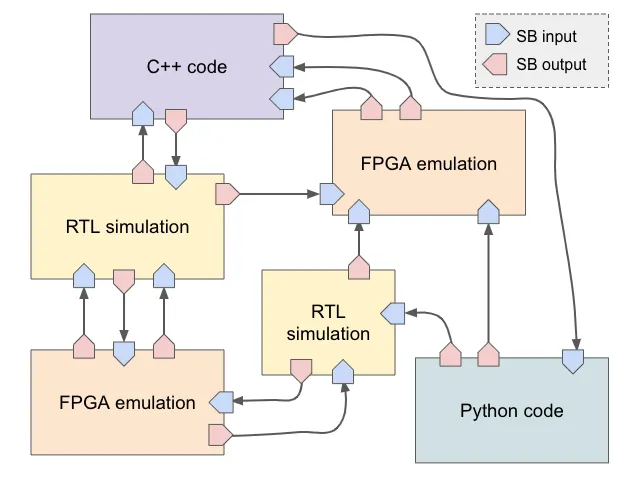

Zero ASIC is thrilled to announce the release of Switchboard, a high-performance open-source framework for communication between RTL simulations, FPGA emulations, Python, and C++. Switchboard makes it possible to simulate large hardware systems in a distributed fashion, using a wide variety of model types, and to interact with the modeled systems from popular software languages.

The framework was designed with performance in mind, using shared memory queues as the underlying communication mechanism. Any number of connections can be active simultaneously, each up to 1 GB/s bandwidth / 200 ns latency. This is fast enough to support real-time interaction with a distributed simulation of chiplets on an active silicon interposer - a result you can try for yourself in our Switchboard-powered emulator app!

From an integration perspective, Switchboard connections can be added to RTL anywhere that there is a ready/valid interface. Simply instantiate a Switchboard input or output module and connect it to the signals of the existing interface. Switchboard supports both Icarus Verilog and Verilator simulators.

In Python, Switchboard connections are established through PySbTx and PySbRx objects. We also provide Python automation for building and running RTL simulations, powered by SiliconCompiler. For performance-critical communication pathways, a C++ interface is provided for sending and receiving Switchboard packets.

Switchboard’s communication scheme is a good fit for using FPGA cards to represent parts of a HW system. We’ve made the memory layout of Switchboard queues simple enough that RTL implemented on an FPGA can directly read and write queues in host memory, and we provide a reference RTL implementation that shows how to set this up.

If this sounds intriguing, please visit our GitHub repository to learn more! The repository contains documentation and examples, including a number of examples showing how Switchboard can be used for block-level testing of components from our recently-released UMI repository. We welcome GitHub issues and pull requests from external contributors!