Andreas Olofsson ·

Simulating a Million-Core System with Switchboard

WOSET is one of the few workshops dedicated to open source EDA. I had the honor of giving the CEDA keynote at the first WOSET conference in 2019 (see “Analyzing the Disruptive Impact of a Silicon Compiler”. This year, I had the opportunity to stand in for Steven Herbst to present our recent work on cloud based wafer-scale emulation. We presented Switchboard at WOSET-24, successfully demonstrating RTL simulation of a million-core system on thousands of cloud compute cores. The total time to build the design and simulate a distributed matrix multiplication was under 15 minutes, demonstrating the agility of our approach.

Sources:

https://github.com/zeroasiccorp/switchboard

Links

Short paper, Long paper, Video

Abstract:

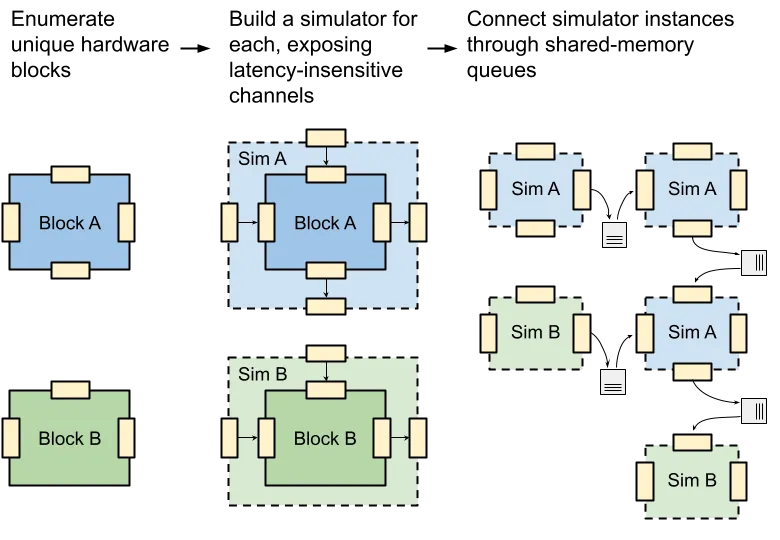

Immense hardware systems are needed to train state-of-the-art machine learning applications such as large language models. The design process for such hardware requires simulation for both architectural exploration and design verification; this can be challenging with traditional simulation approaches due to long build and run times. In this paper, we show how to make simulation tractable for large hardware systems with Switchboard, our open-source modular simulation framework. Switchboard facilitates scalable simulation by connecting prebuilt simulators of reasonably-sized hardware blocks through high-performance shared-memory queues. Each queue conveys a latency-insensitive interface, eliminating the need for explicit synchronization, which can otherwise hamper performance. Using Switchboard, we successfully performed an RTL simulation of a million-core system on thousands of cloud compute cores. The total time to build the design and simulate a distributed matrix multiplication was under 15 minutes, demonstrating the agility of our approach.