Join the Chip Design Revolution

At Zero ASIC our mission is to revolutionize silicon system design. If you are looking to really make a difference, you should considering joining us. There is no other company in the industry quite like it!

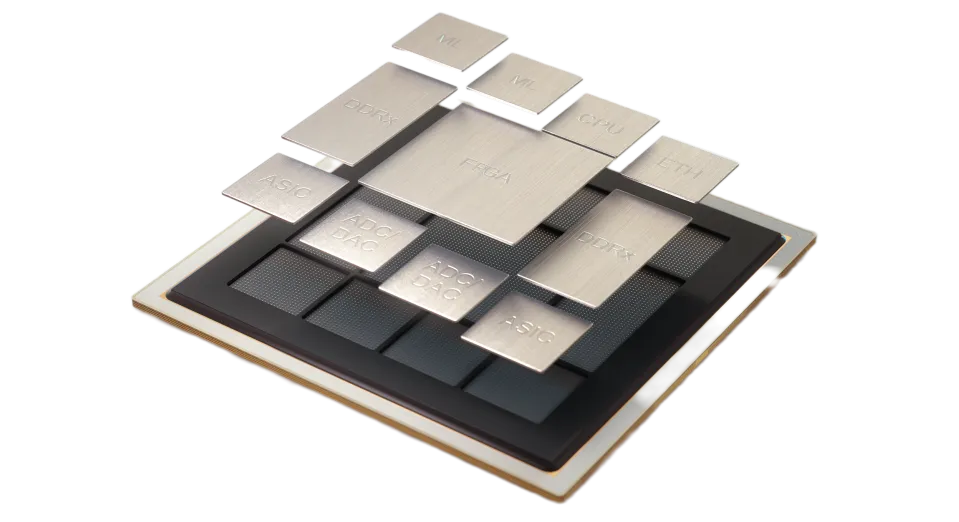

Zero Asic is developing a revolutionary semiconductor design platform that drastically reduces the barriers to chiplet-based design, enabling rapid assembly, simulation, and manufacturing of custom SiP solutions in a matter of hours.

Zero ASIC is building the world’s first composable chiplet platform, enabling billions of unique silicon systems to be assembled in hours from a catalog of off-the-shelf chiplets.

First demonstration of fully standardized chiplets, supporting O(m^n) system permutations (m=library size, n=substrate sockets).

Active 3D silicon substrates that decople compute and networking, enabling LEGO like system composition.

Sub 0.1 pj/bit chiplet communication efficiency.

At Zero ASIC our mission is to revolutionize silicon system design. If you are looking to really make a difference, you should considering joining us. There is no other company in the industry quite like it!

Today Zero ASIC announces the release of a new set of breakthrough open standard eFPGA cores with an advanced set of embedded BRAM and DSPs.

Cambridge, MA – September 17, 2025 – Zero ASIC, a U.S. semiconductor startup on a mission to democratize silicon, today announced the release of WildebeestTM, the world's highest performance open source FPGA synthesis tool. Wildebeest is the first open source logic synthesis solution with Quality of Results (QoR) comparable to proprietary vendor locked tools.

Today Zero ASIC is announcing availability of a production-grade, open-source static timing analysis (STA) flow for FPGAs, enabling analysis of complex multi-clock designs for the open-source FPGA design community.